第二章:总线结构

总线结构

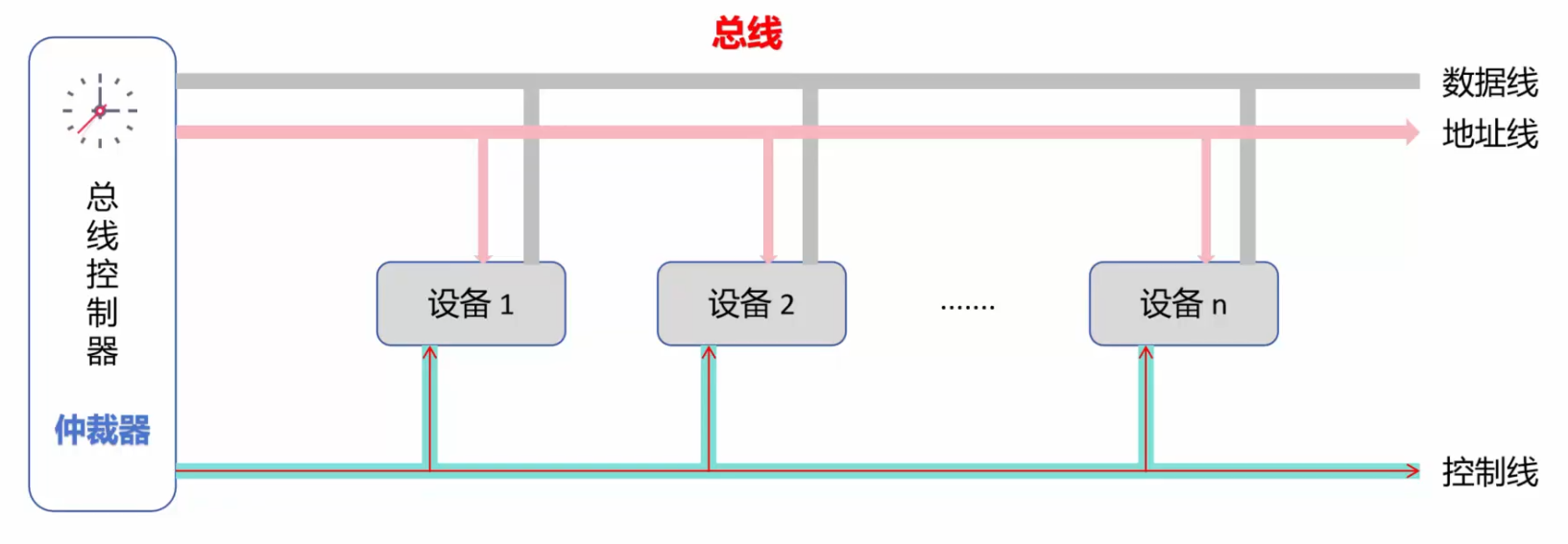

总线是一组为多个部件服务的公共信息传输线路,是计算机内部各个功能部件(如CPU、内存、I/O设备)之间进行数据、地址和控制信息传输的共享通道。

所以,总线是一个公用的通道,他需要一些通用属性:****带宽,仲裁逻辑,总线事务,总线定时,总线标准。

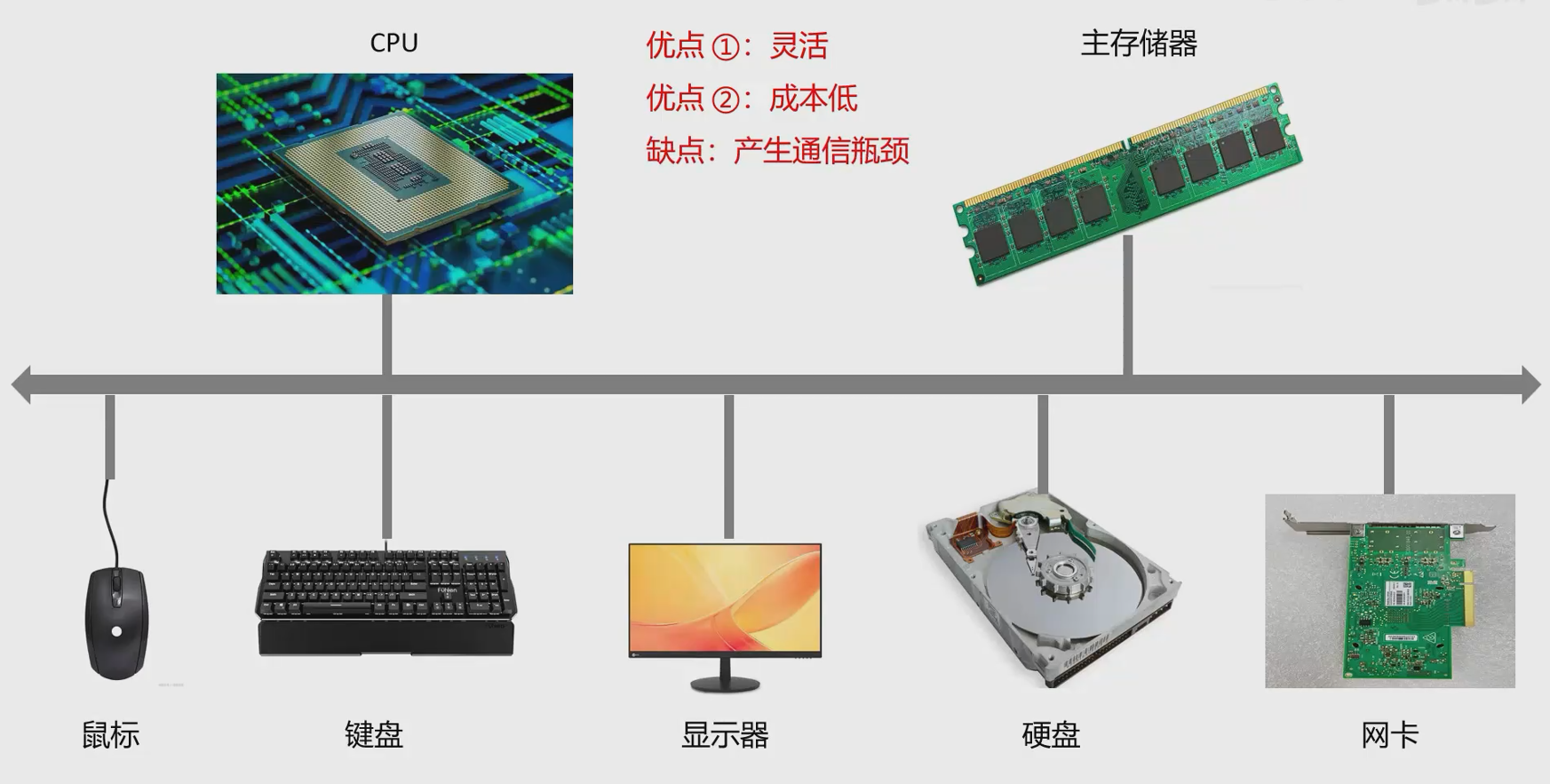

总线在同一时刻在发送相同信息会导致信息冲突,形成通信瓶颈。所以中大型计算机会使用多个总线。

通用属性

通信知识

通信的目的是为了传递数据,信号就是传输载体。

数据又分为连续数据和离散数据,在信号中,连续数据用模拟信号表示,离散数据用数字信号表示。

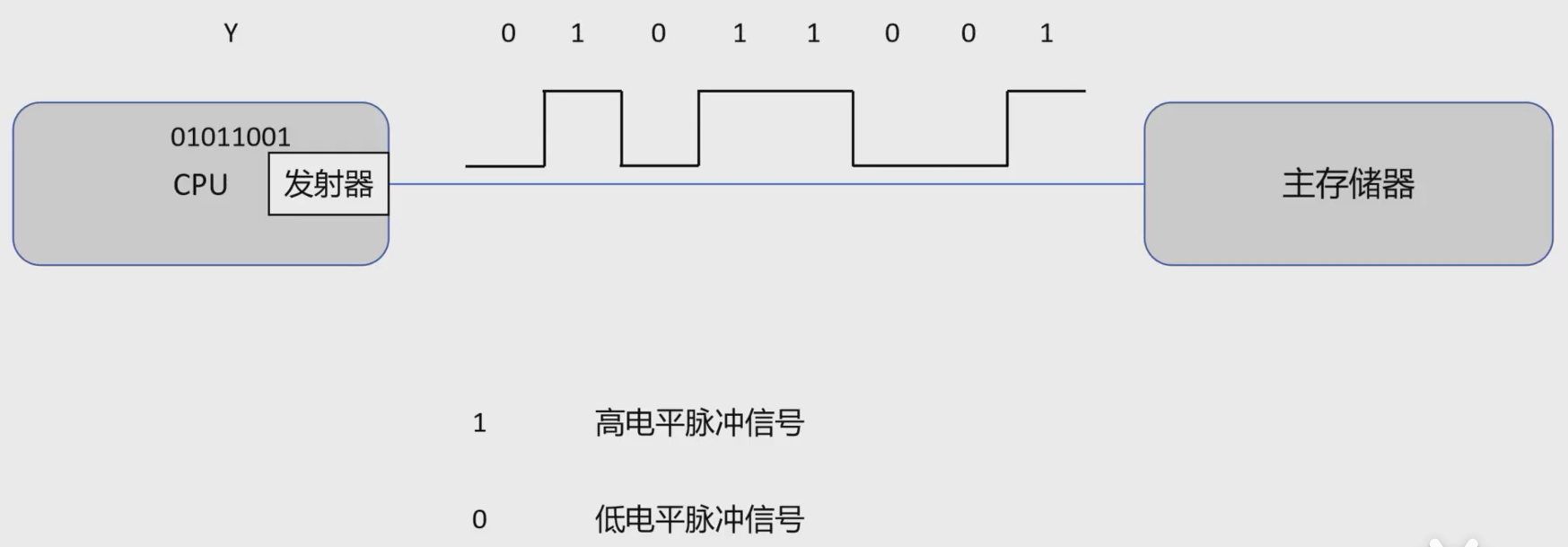

CPU内置一个发射器,能够将二进制码转化为电信号,让别的设备接受,但是这种信号不适用于远距离,需要调制为模拟型号

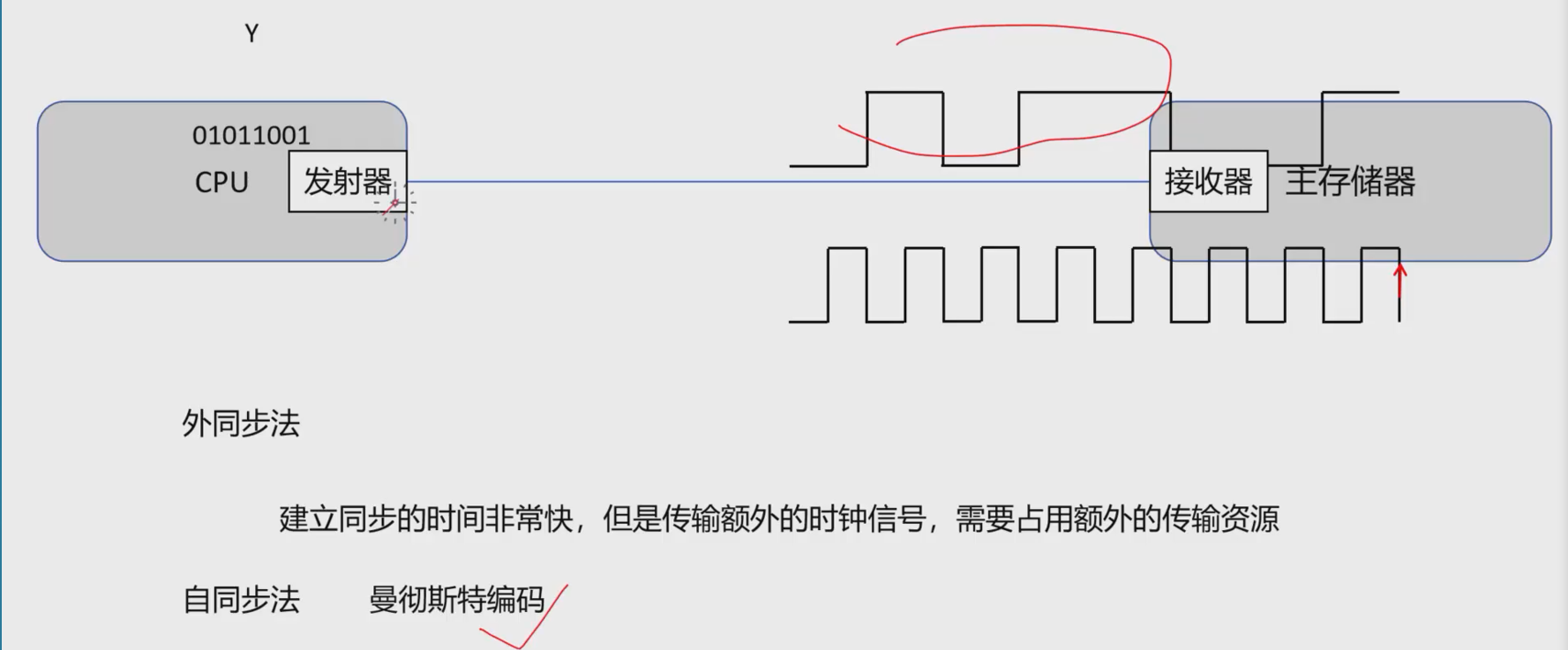

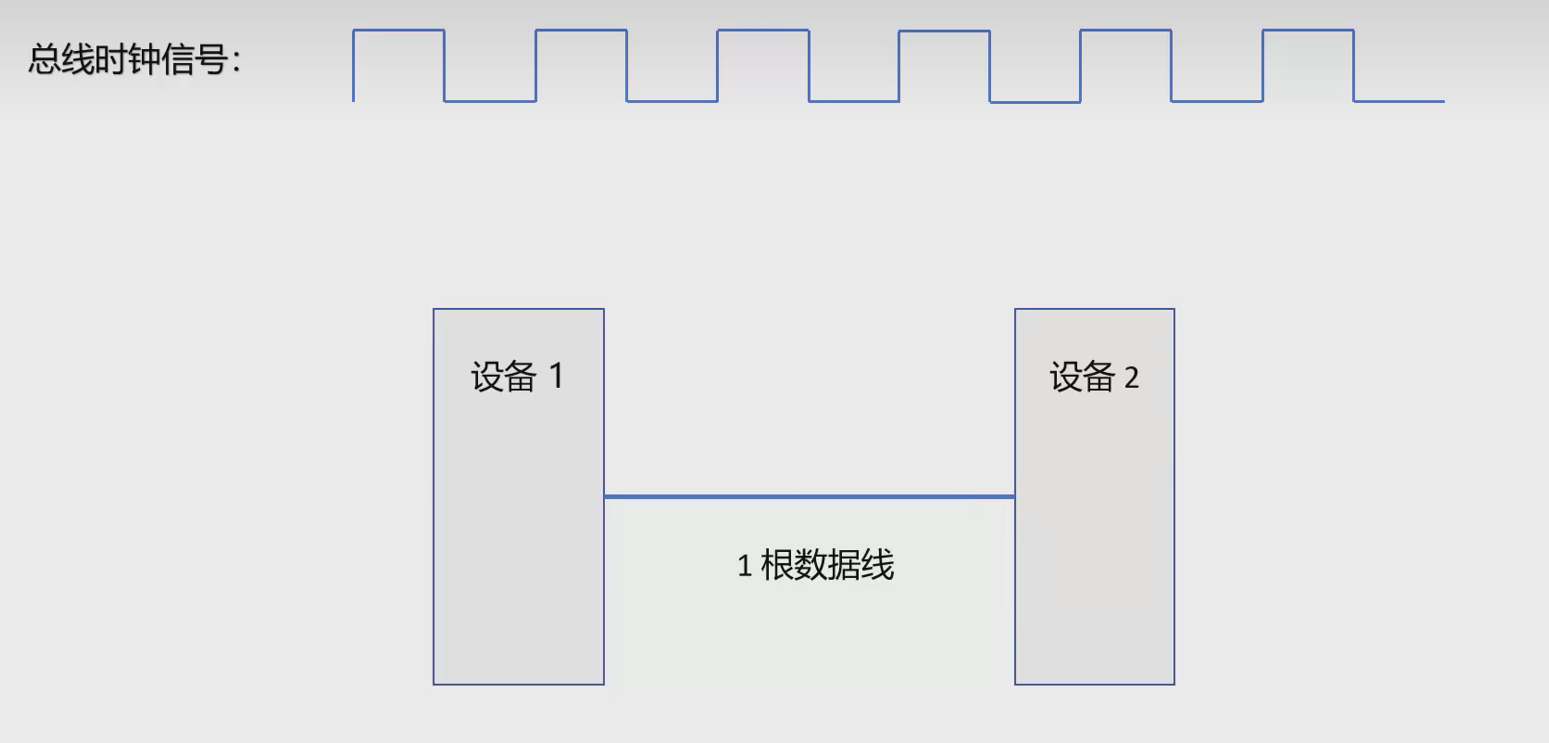

但是,读取的时间是需要控制的,这就由发射器和****接收器中的时钟完成,时钟会发出具有时钟周期的脉冲信号。接收方在接到信号后就知道在一个脉冲信号的周期截获并解析一个二进制码,这种方法称为外同步法。

自同步码后面会提到。

同理,总线也有一个总线控制器,里面有总线时钟来负责同步工作。

带宽

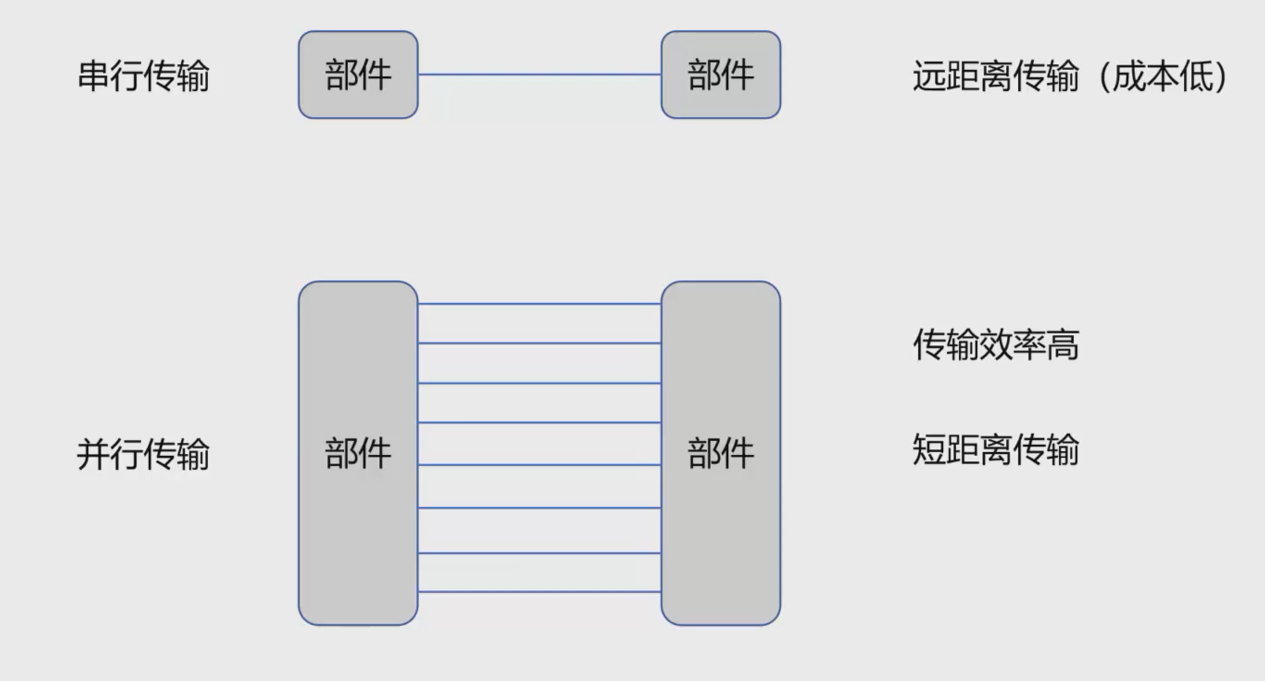

并行运输有缺点,30米以上的长度会导致不同信道的信号到达时间不同,会导致****数据错误

然而总线中有不同类型的支线,支线内部也是****并行传输的。

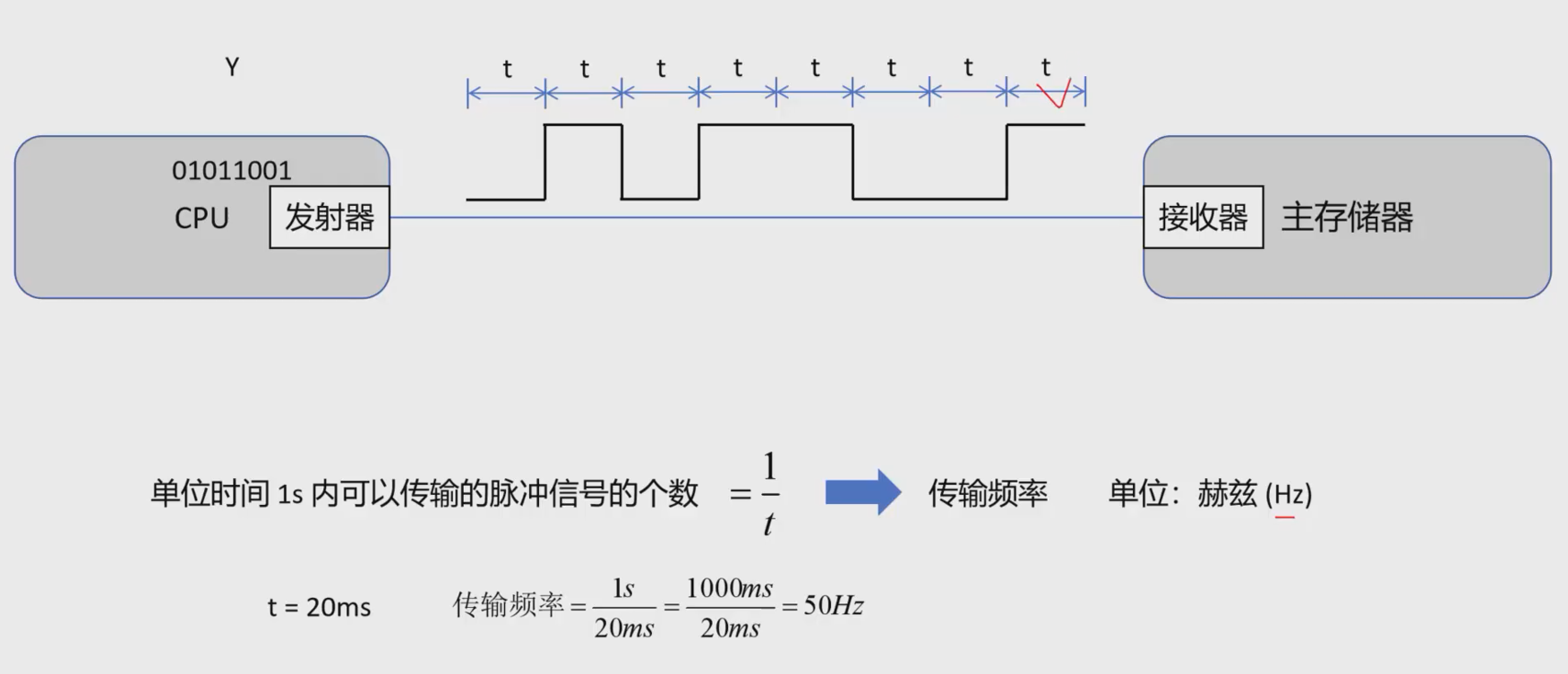

每一个总线有自己的时钟频率,****单位是赫兹hz,100MHz表示每秒传输100M次数据。

所以总线带宽表示总线的最大数据传输率,即****单位时间没最多可以传输的数据量。

$$

\text{总线带宽}=\text{总线宽度}\times\frac{1s}{\text{总线时钟周期}}=\text{总线宽度}\times\text{总线时钟频率}

$$

总线时钟频率是每秒可以发送多少次数据,总线宽度就是每次你能够发送多少位数据。

$$

\text{总线带宽}=32\mathrm{~bit~*~33MHz=(32/8)~B~*~33MHz=~132~MB/s}\quad(1\mathrm{M=10^{6})}

$$

但是现在有的总线在一个总线时钟周期内能够发送2次甚至是4次数据,这样的技术名为DDR技术。

这时候,总线的工作频率就是总线时钟频率的2倍或者4倍。

这时:****总线带宽=总线宽度×总线工作频率=总线宽度×总线时钟频率×数据传输倍数

总线仲裁

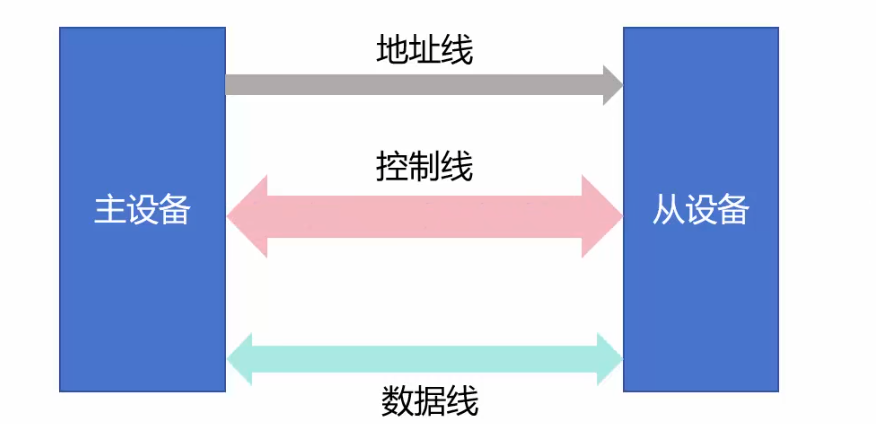

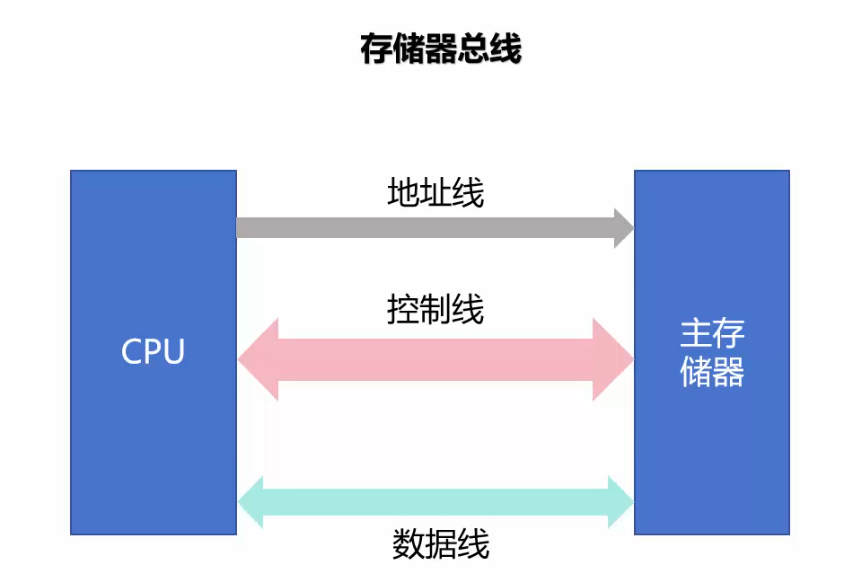

主设备指的是在总线中发射信号的设备,具有总线控制权,从设备是在总线中接收信号的设备,没有总线控制权。

比如,存储器总线中,CPU是主设备,主存是从设备。

主设备想控制从设备需要先向总线控制器发送信号,得到同意信号后才能拿到控制权,才能通过总线通信。如果多个主设备申请,总线需要仲裁需要确定同意哪些申请。

仲裁分为****集中式仲裁和分布式仲裁。

集中式仲裁又分为****链式查询方式,计时器查询方式和独立请求方式。

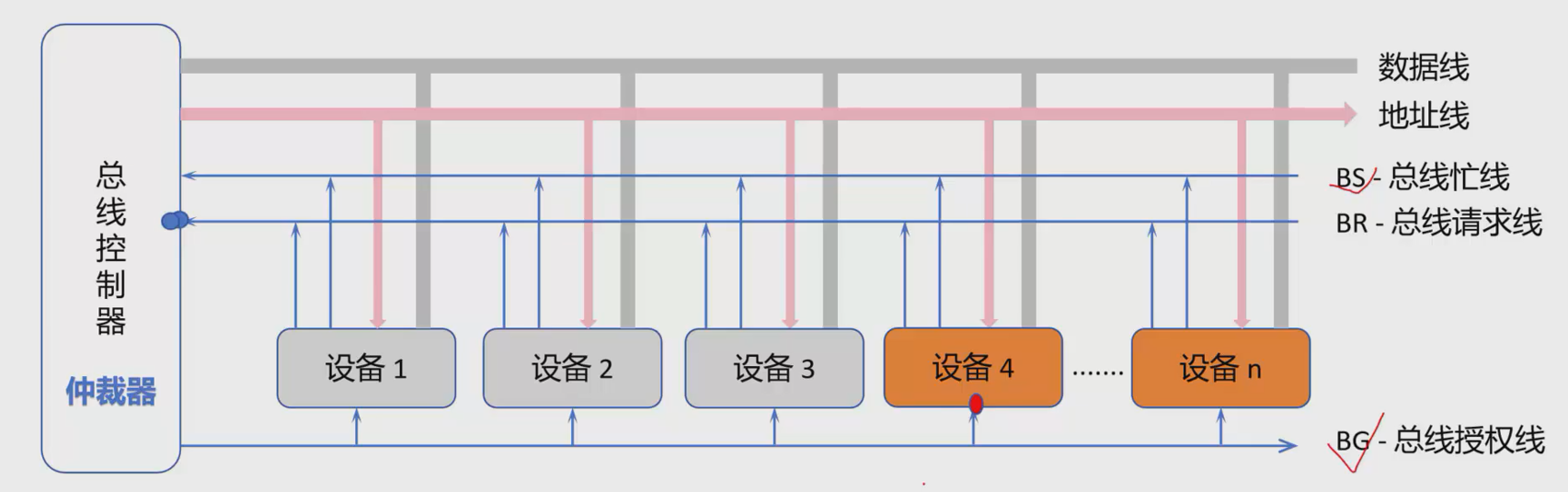

链式查询方式:

设备4和设备n发送使用申请,随即总线授权线会逐个检查设备是否发送过申请,如果发送过就同意申请。这样的方式使用几根线就能实现一定优先次序的总线仲裁,容易扩充设备。但是对电路敏感很故障,而且查询链的次序很固定。

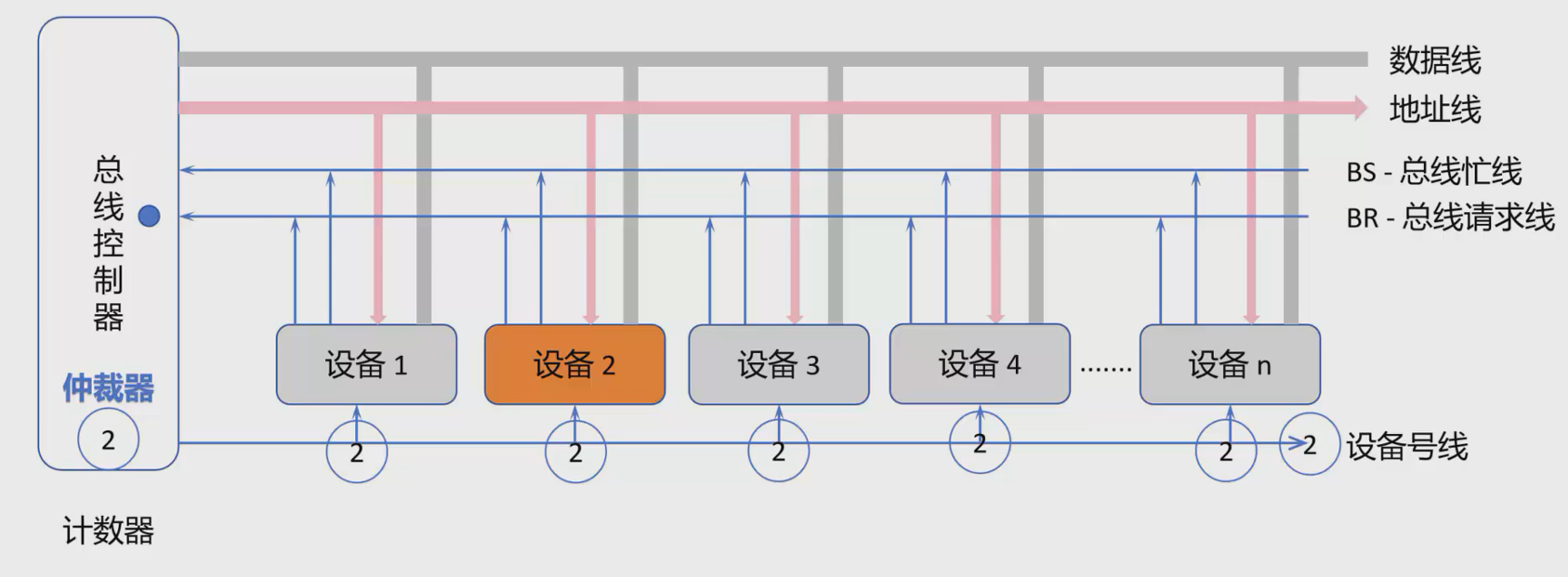

计数器定时查询:

总线控制器内置一个计数器,初始为1,如果设备2发送了总线请求,总线控制器会将1这个数值通过设备号线发送到每个设备(也就是广播),随即检查设备号与发送的数值相等的设备有没有发送过请求,如果有就同意,如果没有就让计数器自增然后向所有设备广播2,这个数值,检查到设备2并同意之后,总线忙,该阶段计数器不会变化。总线被设备2解除占用后,计数器恢复自增功能,变为3继续检查。

优点是优先级是相同的,计数器初始值可以通过程序设置,但是控制线数量很多,如果有15个设备,至少需要4位二进制,2^4 = 16。n台设备需要log2(n)条数据线

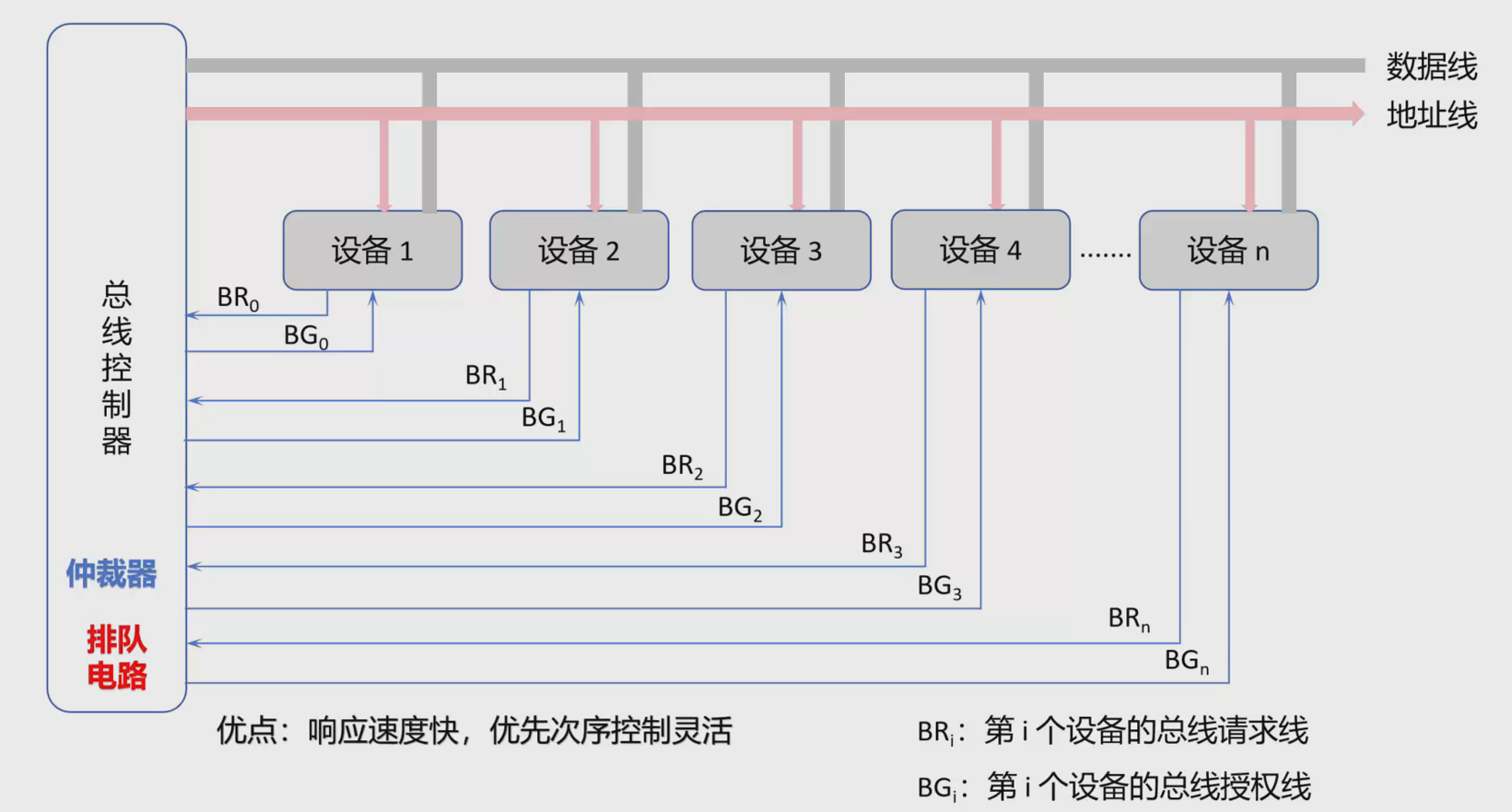

独立请求方式(使用较多):

每个设备都有独立的申请线路,总线控制器内部有一个排队电路,先接收到申请就先通过,先来后到,忙完下一个。

优点是响应速度很快,次序控制灵活,但是控制线数量很多,行线复杂,n台设备需要2n条控制线

总线事务周期

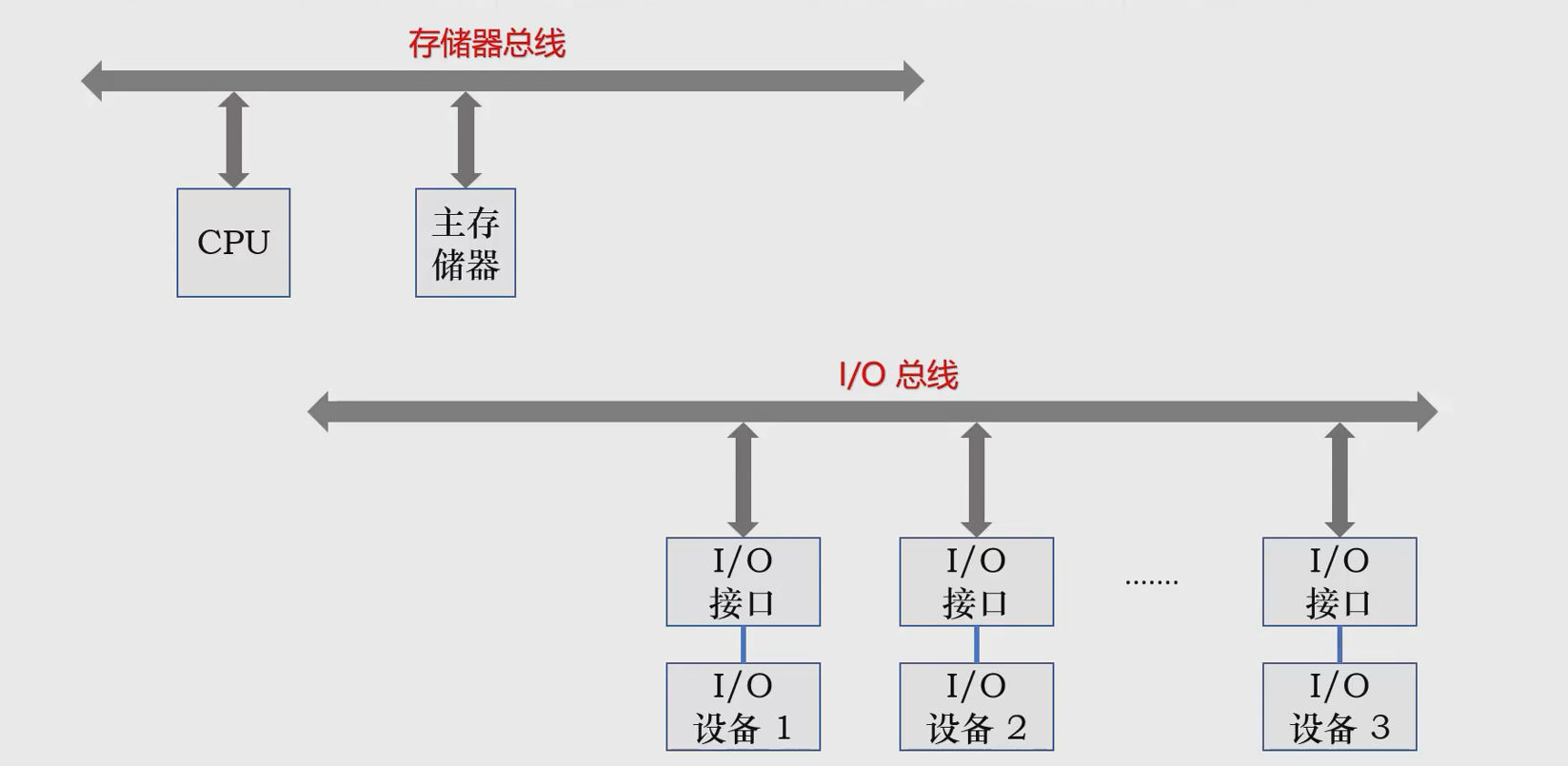

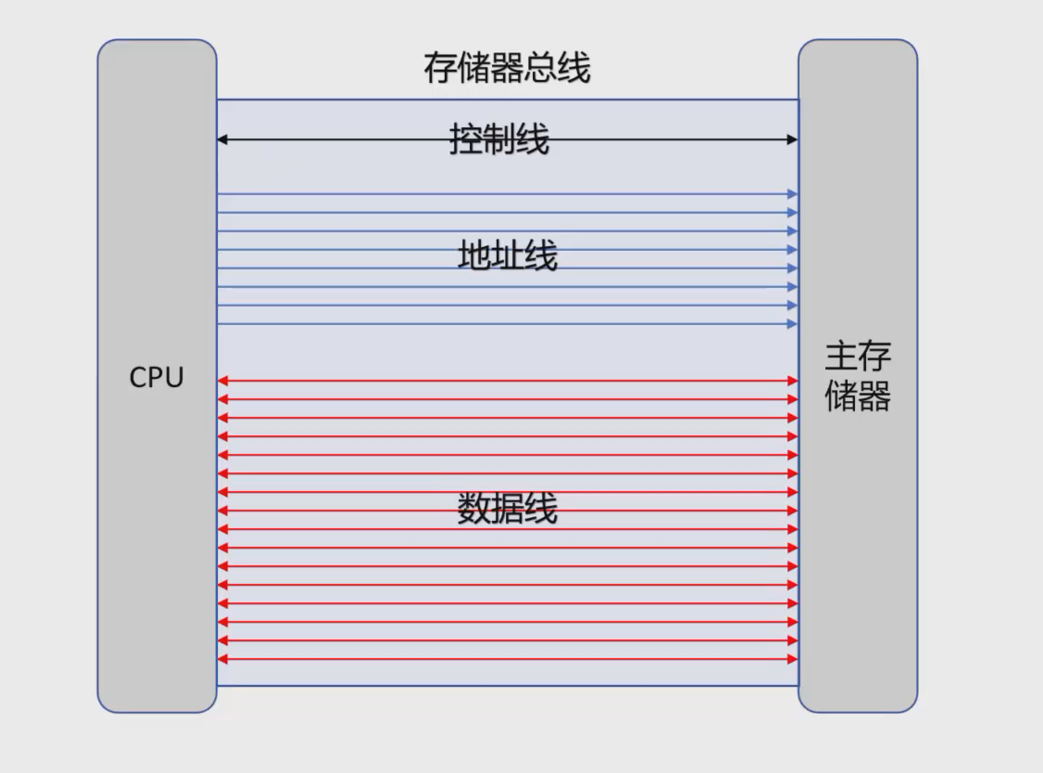

数据线是双向的,用于传输数据,地址线传输数据对应的地址,控制线传输控制信息,比如时钟信号等,控制线整体上是双向的。

总线周期就是完成一次总线操作的时间。

一个周期包括四个阶段。

1.申请分配阶段

主设备向总线控制器发送申请,总线仲裁器将总线控制权移交到主设备。

2.寻址阶段

主设备通过总线发送从设备地址,启动从设备

3.数据传输阶段

主设备与从设备进行数据交换

4.结束

主设备的信息从总线中撤除,让出总线控制权

总线定时

总线周期内有很多操作时间:****发送地址,发送命令,提供数据,撤销命令,撤销数据。

总线定时是为了解决这些操作事件在一个周期内的先后次序关系。

定时方式有好几种,分为同步定时和异步定时。

同步定时:

时钟信号线会发送4个时钟信号

以主设备读取从设备数据为例

T1:主设备发送从设备地址

T2:主设备发送读取从设备的命令

T3:从设备提供数据

T4:主从设备撤销命令,撤销数据

这里没有申请分配阶段

这样的定时方式有很高的传输频率但属于强制性同步,如果有读写很慢的部件他会拖慢整个读写速度。

适用于总线长度短,各设备存取时间差不多的情况。

异步定时

异步定时允许总线上设备存储时间不一致

数据交换的过程是

主设备将地址发送到地址线等地址信号稳定后,通过控制线发送读命令到从设备,从设备将数据放到数据线,等到数据线信号稳定后,从设备使用一个确认线告知主设备连接安全,数据交换结束后,从设备撤销数据线,主设备撤销地址线

可以看出:后一个操作事件出现在总线上的时刻取决于前一个操作事件出现的时刻

异步请求有三种

- 异步定时(不互锁)

- 主设备向从设备发送请求,等待一段时间后,不管有没有应答,撤销请求信号,就执行其他任务,从设备接收到请求,将数据放到数据线上,将确认通知发送到主设备,等待一段时间,撤销通知信号,然后执行其他任务。

- 异步定时(半互锁)

- 主设备发送请求,等待从设备应答,从设备应答,从设备将数据放到数据线中,从设备等待一定事件后离开并执行其他任务

- 异步定时(全互锁)

- 主从设备发出的信息必须等待回复,否则不能撤销信号,这就是二者的互相锁定

CPU和主存同步和异步都可以,有些读写速度差别过大的只能用异步,用同步会严重拖慢CPU速度。

总线数据传输方式

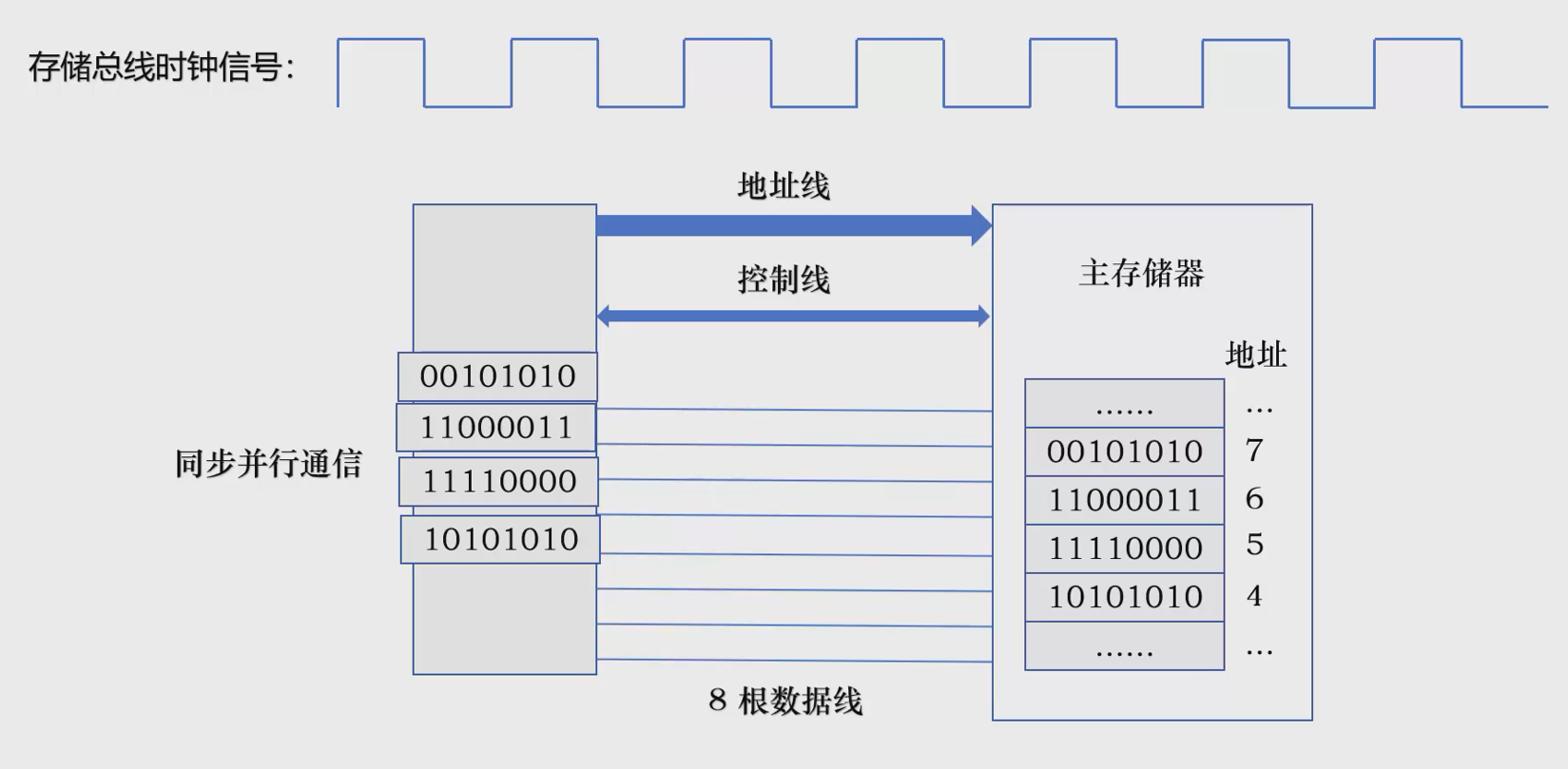

分为串行和并行,串行就是一次只能传输一位二进制信息,并行就是一次能够传输多为二进制信息,这和同步异步一起可以理解为4种场景。

也就是:

- 同步串行通信

- 异步串行通信

- 同步并行通信

- 异步并行通信

同步串行通信

外同步法:每个时钟周期发送一位二进制

外同步法:每个时钟周期发送一位二进制

自同步法:在每个数据元的头加上同步字符来同步

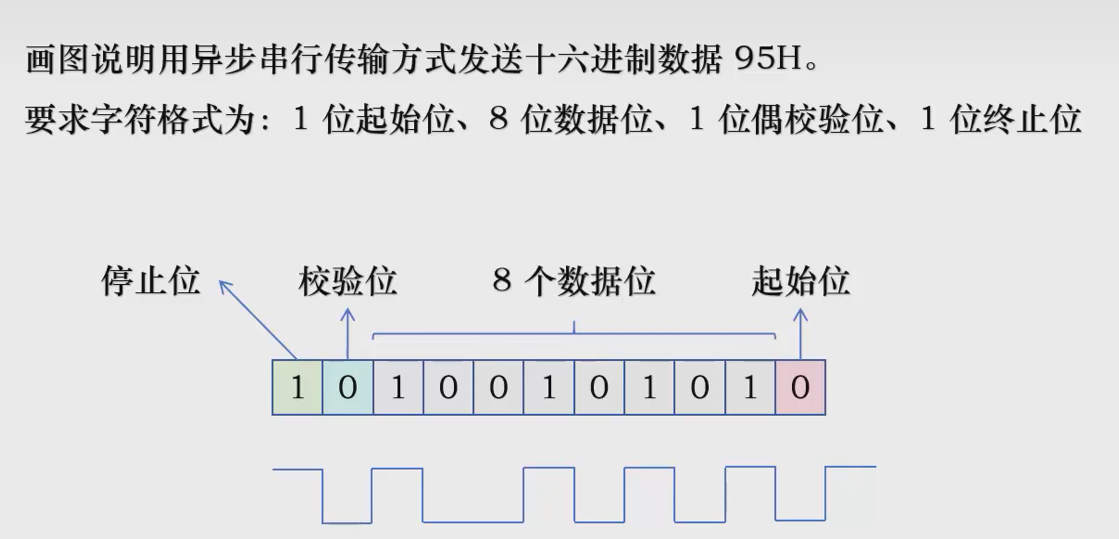

异步串行通信(这很重要)

现代大多数总线都是这种通信模式,这很重要。

不需要同步时钟,以字符为单位传输

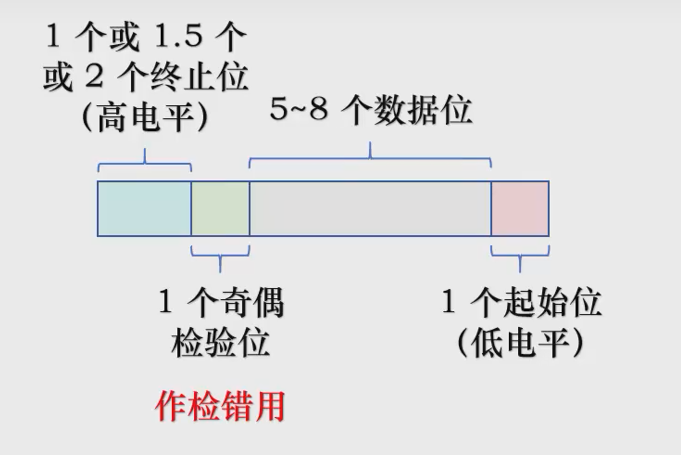

字符结构示意图:

奇偶校验是为了检查传输是否有错误,分为奇校验和偶校验。

奇偶校验位是一个附加位,其值(0或1)使得包括校验位在内的整个数据单元中“1”的个数为奇数(奇校验)或偶数(偶校验)。

比如奇校验数据1011001****1,加粗是校验位可以看到,为了使包括校验位在内的1的数量为奇数,校验位只能是1。如果传输中出错,某一个1变为0,那就统计的数量时不再是奇数。

但是如果出错两个,那就检查不出来,更别提纠正。

数据传输速率用波特率来衡量。

波特率:单位时间内传输的二进制数据位数,单位bps(位/秒)

突发传输

如果是非突发传输:命令周期为T

T1:传起始地址

T2:传读命令

T3:读取4地址的数据

T4:撤销命令和地址

以后每一位数据都要这么干,要花4个周期。

如果是突发传输

T1:传地址

T2:传控制命令

T3:传一个数据

T4T5T6:传剩下三个数据

T7:撤销命令,结束传输

这么来就少了很多个周期,传输效率很高。

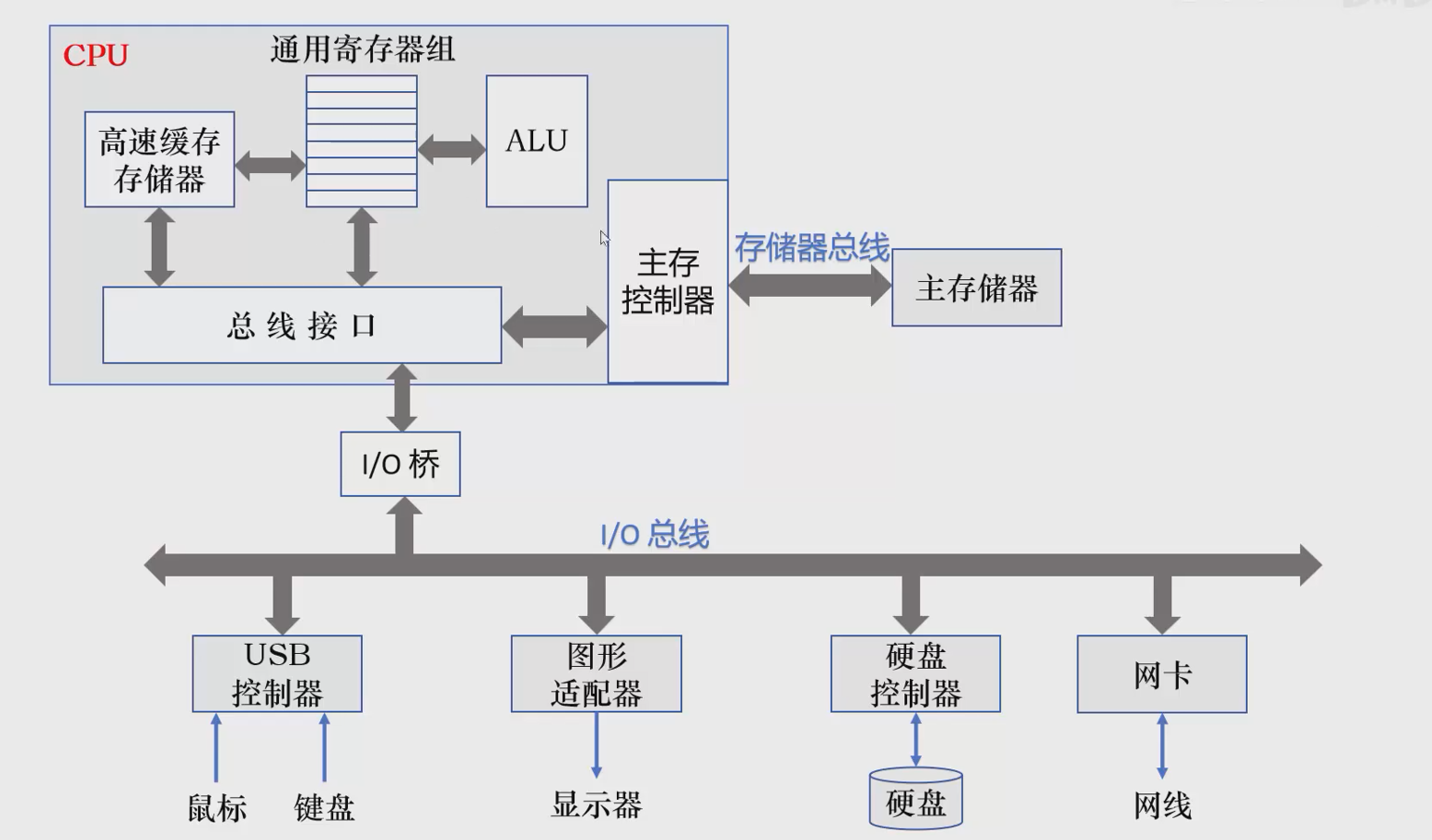

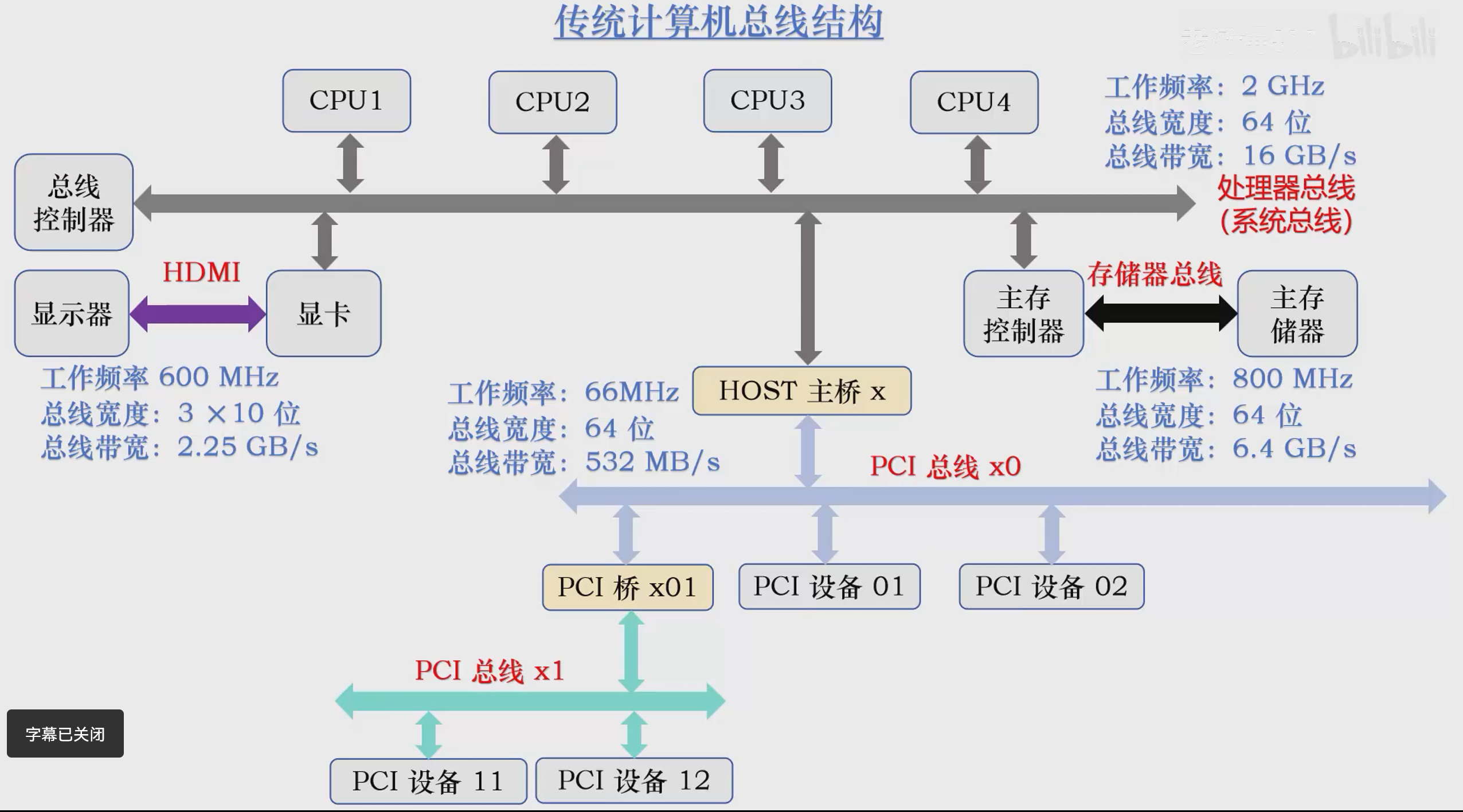

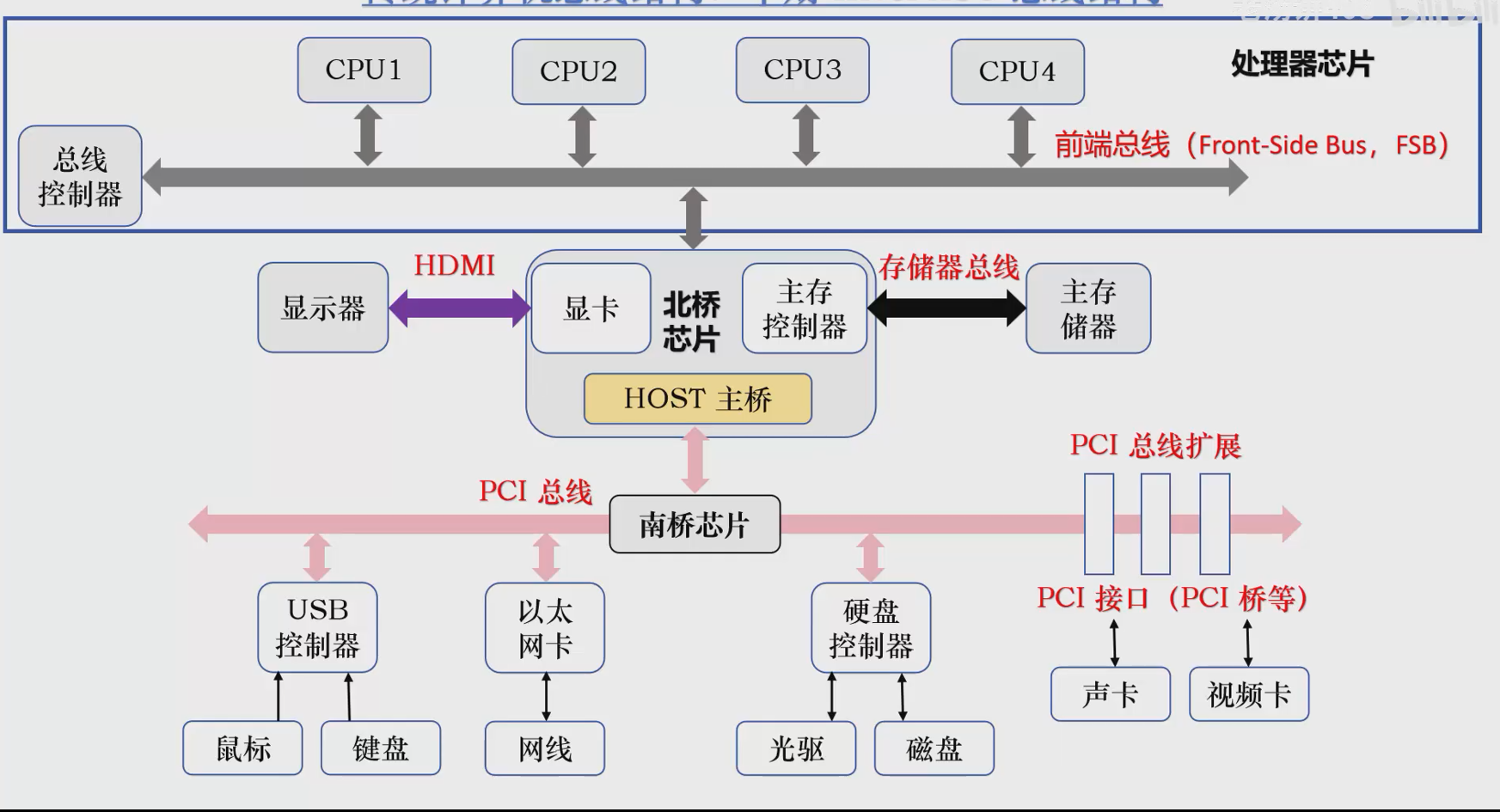

传统计算机的总线结构

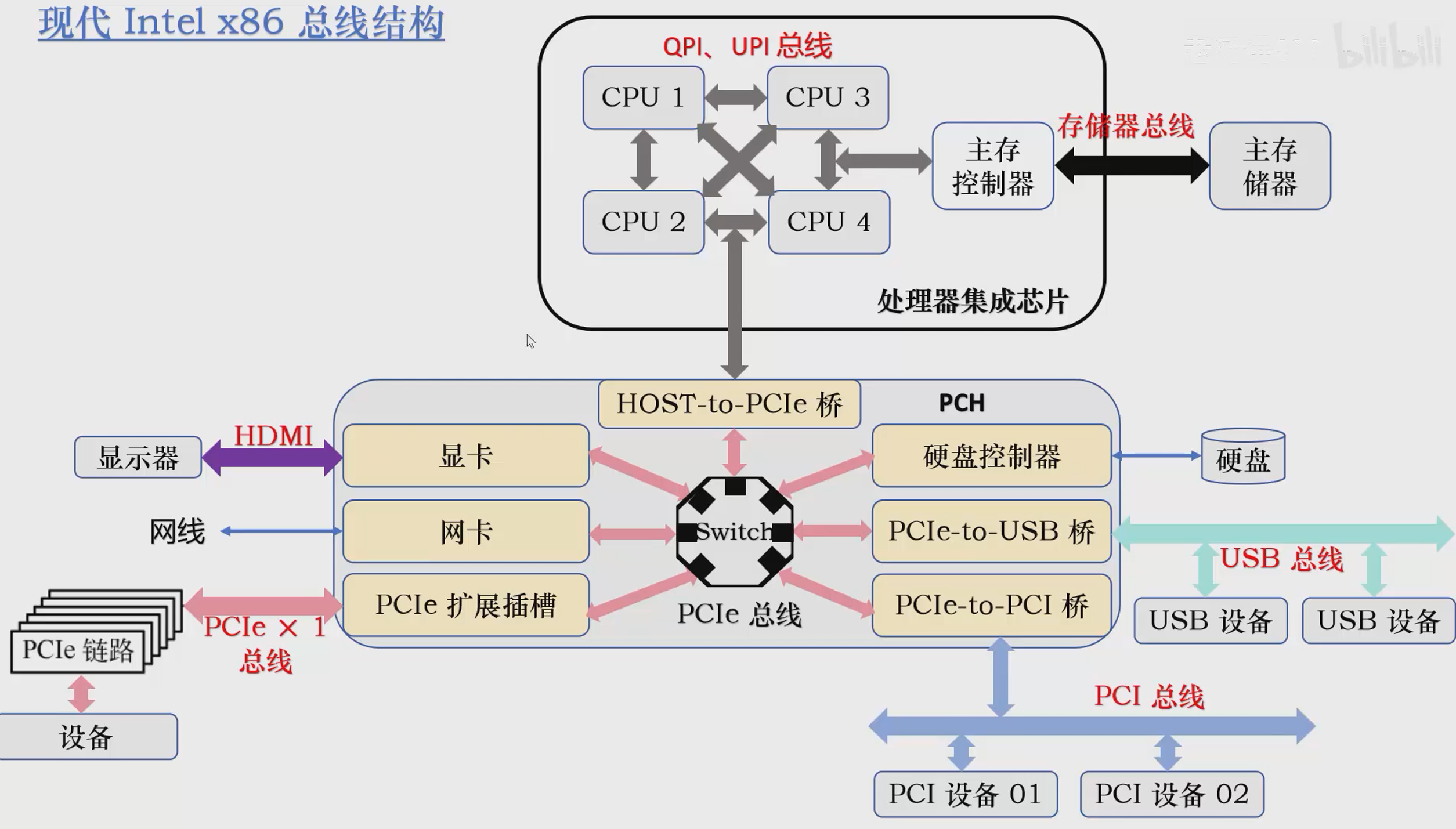

现代计算机的总线结构

可以看到本来CPU之间是共享链接,在新的结构中是独立链接

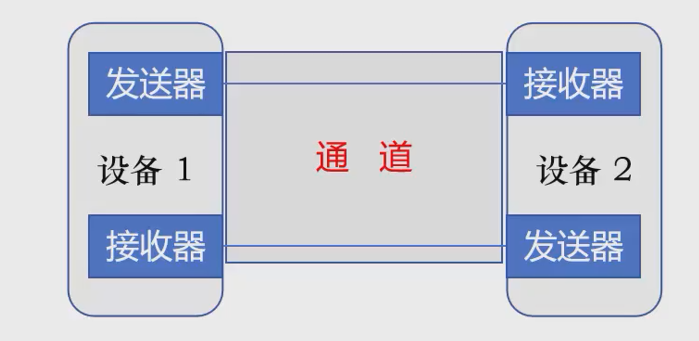

PCle总线是一个串行的点对点总线,全双工。

PCIe的“全双工”是指****每个链路(Lane)由独立的发送和接收通道组成,支持同时双向传输

总体结构